เวอร์ชัน

7

เวอร์ชัน

7

ชื่อแพ็กเกจ

com.faadooengineers.free_vlsidesign

ชื่อแพ็กเกจ

com.faadooengineers.free_vlsidesign

หมวดหมู่

การเรียนรู้การศึกษา

หมวดหมู่

การเรียนรู้การศึกษา

ขนาด

11.3MB

ขนาด

11.3MB

ทำคู่มือฟรีของ VLSI พร้อมไดอะแกรมและกราฟ

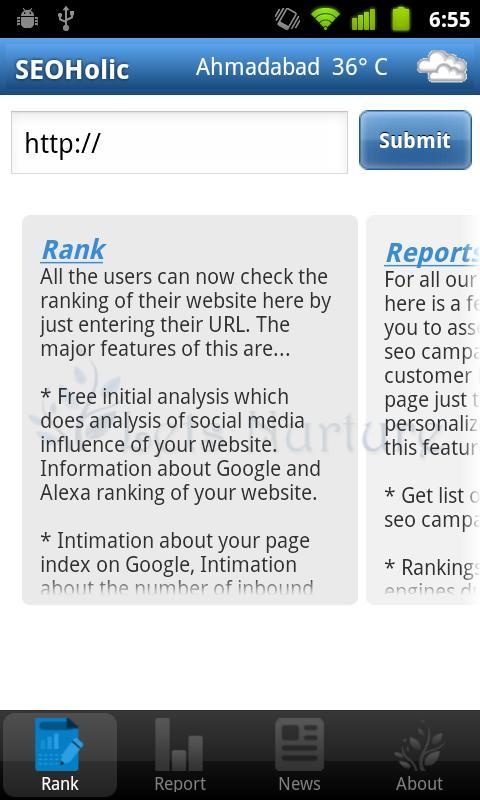

แอพนี้เป็นคู่มือฟรีของ VLSI พร้อมไดอะแกรมและกราฟ มันเป็นส่วนหนึ่งของการศึกษาด้านวิศวกรรมอิเล็กทรอนิกส์และการสื่อสารซึ่งนำหัวข้อสำคัญบันทึกข่าวและบล็อกในเรื่องนี้ ดาวน์โหลดแอพเป็นคู่มืออ้างอิงอย่างรวดเร็วและ ebook เกี่ยวกับวิชาวิศวกรรมอิเล็กทรอนิกส์และการสื่อสารนี้

แอพครอบคลุมมากกว่า 90 หัวข้อของการออกแบบ VLSI โดยละเอียด หัวข้อเหล่านี้แบ่งออกเป็น 5 หน่วย

คุณสามารถผ่านและประสบความสำเร็จในการสอบหรือการสัมภาษณ์ได้อย่างง่ายดายแอปให้การแก้ไขอย่างรวดเร็วและอ้างอิงถึงหัวข้อต่างๆเช่นการ์ดแฟลชรายละเอียด

แต่ละหัวข้อเสร็จสมบูรณ์ด้วยไดอะแกรมสมการและรูปแบบอื่น ๆ ของการเป็นตัวแทนกราฟิกเพื่อความเข้าใจที่ง่าย บางหัวข้อที่กล่าวถึงในแอปพลิเคชันนี้คือ:

1. ความทรงจำเซมิคอนดักเตอร์: บทนำและประเภท

2. อ่านเฉพาะหน่วยความจำ (ROM)

3. สามเซลล์ DRAM ทรานซิสเตอร์

4. หนึ่งเซลล์ DRAM TRANSISTOR

5. หน่วยความจำแฟลช

6. ต่ำ - วงจรลอจิก CMOS พลังงาน: บทนำ

7. การออกแบบอินเวอร์เตอร์ CMOS

8. อินเวอร์เตอร์ MOS: บทนำเกี่ยวกับลักษณะการสลับ

9. เทคนิคการสแกน

10. เทคนิคการทดสอบตนเองในตัว (BIST)

11. ความคาดหวังทางประวัติศาสตร์ของการออกแบบ VLSI: กฎหมายของมัวร์

12. การจำแนกประเภทของวงจรดิจิตอล CMOS

13. ตัวอย่างการออกแบบวงจร

14. วิธีการออกแบบ VLSI

15. การออกแบบการออกแบบ VLSI

16. ลำดับชั้นการออกแบบ

17. แนวคิดเรื่องความสม่ำเสมอโมดูลาร์และสถานที่

18. การประดิษฐ์ CMOS

19. การไหลของกระบวนการผลิต: ขั้นตอนพื้นฐาน

20. การผลิตทรานซิสเตอร์ NMOS

21. การผลิต CMOS: กระบวนการ P-well

22. การผลิต CMOS: กระบวนการ n-well

23. CMOS Fabrication: Twin Tub Process

24. ไดอะแกรมแท่งและการออกแบบเค้าโครงหน้ากาก

25. ทรานซิสเตอร์ MOS: โครงสร้างทางกายภาพ

26. ระบบ MOS ภายใต้อคติภายนอก

27. โครงสร้างและการทำงานของ MOSFET

28. แรงดันไฟฟ้าเกณฑ์

29. ลักษณะแรงดันไฟฟ้าปัจจุบันของ MOSFET

30. การปรับขนาด MOSFET

31. ผลของการปรับขนาด

32. เอฟเฟกต์เรขาคณิตขนาดเล็ก

33. mos capacitances

34. อินเวอร์เตอร์ MOS

35. ลักษณะการถ่ายโอนแรงดันไฟฟ้า (VTC) ของอินเวอร์เตอร์ MOS

36. อินเวอร์เตอร์ที่มีโหลด n-type mosfet

37. อินเวอร์เตอร์โหลดตัวต้านทาน

38. การออกแบบอินเวอร์เตอร์โหลดลดลง

39. อินเวอร์เตอร์ CMOS

40. คำจำกัดความเวลาหน่วงเวลา

41. การคำนวณเวลาหน่วง

42. การออกแบบอินเวอร์เตอร์ที่มีข้อ จำกัด การหน่วงเวลา: ตัวอย่าง

43. วงจรลอจิกแบบผสมผสาน MOS: บทนำ

44. วงจรลอจิก MOS พร้อมการสูญเสีย NMOS โหลด: สองอินพุตหรือเกต

45. วงจรลอจิก MOS ที่มีการสูญเสีย NMOS โหลด: ทั่วไปหรือโครงสร้างที่มีหลายอินพุต

46. MOS Logic Circuits ที่มีการสูญเสีย NMOS โหลด: การวิเคราะห์ชั่วคราวของ NOR GATE

47. วงจรลอจิก MOS ที่มีการสูญเสีย NMOS โหลด: เกต NAND สองอินพุต

48. วงจรลอจิก MOS ที่มีการสูญเสีย NMOS โหลด: โครงสร้าง NAND ทั่วไปที่มีหลายอินพุต

49. MOS Logic Circuits ที่มีการสูญเสีย NMOS โหลด: การวิเคราะห์ชั่วคราวของประตู NAND

50. วงจรลอจิก CMOS: NOR2 (สองอินพุตหรือ) เกท

51. CMOS NAND2 (สองอินพุต NAND) ประตู

52. เลย์เอาต์ของประตูตรรกะ CMOS อย่างง่าย

53. วงจรลอจิกที่ซับซ้อน

54. ประตูตรรกะ CMOS ที่ซับซ้อน

55. เลย์เอาต์ของประตูตรรกะ CMOS ที่ซับซ้อน

56. Aoi และ Oai Gates

57. ประตูเทียม NMOS

58. CMOS วงจรเต็มรูปแบบและพกพา Ripple Adder

59. ประตูส่งสัญญาณ CMOS (ผ่านประตู)

60. ตรรกะการแปลผ่าน (CPL) เสริม

61. วงจรลอจิก MOS ตามลำดับ: บทนำ

62. พฤติกรรมขององค์ประกอบ bistable

63. วงจรสลัก SR

64. ล็อค SR โอเวอร์คล็อก

65. jk latch

66. Master-Slave Flip-Flop

67. CMOS D-LATCH และ FLIP-FLOP

68. วงจรลอจิกแบบไดนามิก: บทนำ

69. หลักการพื้นฐานของวงจรทรานซิสเตอร์ผ่าน

หัวข้อทั้งหมดไม่ได้อยู่ในรายการเนื่องจากข้อ จำกัด ของตัวละครที่กำหนดโดย Play Store